Preparing target connection

Prior to running or debugging the application, you must:

- Establish a physical connection between the host and target

- Prepare an execution environment on the target, and

- Establish a logical debug channel between the host debugger and execution environment

Physical target connection

For most target platform(s) (FPGAs boards), physical target connection is achieved via one of the following means:

- Host computer and target platform connected via USB

- Target platform installed as a PCIe device on host computer

- Host computer connected to target via secure VPN (cloud native)

For most cases, a USB cable is used to connect the host system to the target platform

Preparing execution environment

A binary image (bitfile) containing the hardware design of the system-on-chip that runs the embedded program will need to be downloaded and programmed on the FPGAs or hardware-assisted verification systems (HAVS) target.

For ASIC target platforms, no additional preparation is needed.

To program a bitfile to the specific board, click on the flash icon ![]() on the toolbar of XploR Studio IDE.

on the toolbar of XploR Studio IDE.

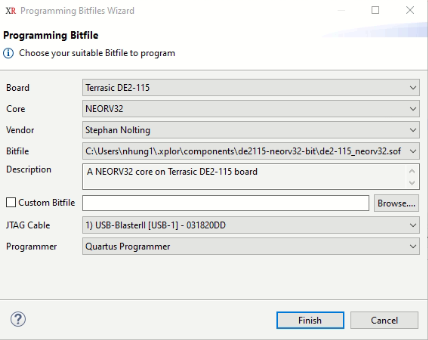

The Programming Bitfile dialog appears to make it easier to select Bitfiles from different vendors:

The images show the selected Bitfile is de2-115_neorv32.sof, which is the bitfile for Terrasic DE2-115 FPGA board from Stephan Nolting vendor and the tool used for programming board is quartus_pgm (Quartus Programmer).

To program with more bitfiles, install IP Component from different vendors and select the desired bitfile from the list.

Feedback

Was this page helpful?

Glad to hear it! Please tell us how we can improve.

Sorry to hear that. Please tell us how we can improve.